超大规模集成电路(超LSI)—直在继续不断地向前发展着。其发展趋势可以从代表最尖端技术的MOS存贮器的变化情况中看出来。自从1970年开发出1K DRAM以来,到今天为止,其集成度是以每3年增加4倍的速度发展着的,仅经过15年就已增长了1,000倍。从去年末的IEDM'84到今年2月的ISSCC'85期间,日本有关各公司先后发布了兆位DRAM技术的开发状况,可以说新的超LSI时代应该是兆位时代的序幕已经拉开了。

M位DRAM元件的结构

1M DRAM的设计规范(最小尺寸)为1.2 ~ 1.3 μm,这个值与256K DRAM的比例值大体上一样。元件的面积为20 ~ 35 μm2,比256K DRAM缩小约1/3,因此,在电容结构上采用了开沟型和积层型(迭加式)等新的结构。也有的仍采用通常平面结构式,但即使将栅膜厚度做成10 ~ 12 nm,元件的面积还是稍有增大,此外,对DRAM,要求其应具有高度可靠性和适宜于大量生产性。因此,希望能尽量减少新技术引入过程中因工艺熟练和适宜性等因素造成的成品率下降问题。和256 KDRAM生产不同,1M DRAM的器件工艺技术等,还没有统一的规程,各公司各有不同。

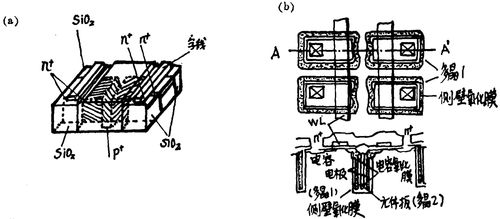

如果从目前DRAM技术的发展趋势来预测今后的发展前景的话,估计三年后将要开发出的4M DRAM设计规范应为0.8 μm,元件面积大约为14 μm2。一旦达到这样小的面积,如果不能开发出新的电介质材料,就不能再采用传统的平面器件结构工艺了。在4M DRAM中既要考虑到元件间的分离问题又要考虑到微细化问题,有人报导了三种4M DRAM元件结构,即:BIC型(埋层绝缘电容型);IVEC型(共用绝缘的垂直电容型);FCC型(场电容型)。它们都属于开沟型结构,避免了过去元件之间存在的相互影响的问题。(图1.(a)(b))

图1:4M DRAM存贮 器元件结构(a,b)

采用BIC结构的元件能达到0.8 μm的规范,元件面积为9 ~ 10 μm2,但沟槽深度必须达到5 μm左右才能达到上述要求的标准,但若将IVEC型元件以0.5 μm规格设计、元件面积就有可能作到估计这对16M DRAM元件也是适用的。而且,与一般开沟型电容相比,获得同样容量时所需开的沟槽要浅些。比如,采用上述IVEC型0.5 μm规格,沟深2.2 μm时,用一般的元件结构的沟深则要达到3.8 μm。因此,若以0.8 μm规范设计FCC存贮器元件时,元件面积则可以达到沟深2 μm的水平。

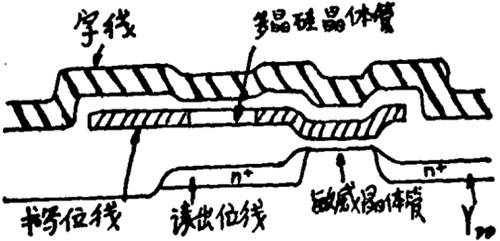

如果把对4M DRAM的推断也适用到16M DRAM器件上的话,则其设计规格就成了0.5 μm,元件面积则可达到6 μm2。上述这些新型结构当然也适用于与4M DRAM有同样开沟结构的元件。例如,采用这类开沟结构的使用SOI技术的新型TITE元件(横向注入双电极元件)等就进入了实用化的阶段。(图2)。

图2:使用SOI技术的TITE元件结构

微细化中离密度化和可靠性问题

到了兆位时代,为了谋求高密度化,设计上采用了从1μm到亚微米级的最小规范,以图尽可能地增大芯片面积和提高成品率,降低成本。一般的LSI都是将器件尺寸、线路图尺寸缩小来使器件高集成化,使得性能与价格之比大幅度的改善,使可靠性大幅度地提高。可是,如果成为超LSI,由于微细化也带来了一些新的问题。一是由于元件尺寸的缩小而出现的α线软漂移问题;二是微细化的CMOS的闭锁超载现象;三是由于短沟道FKT的热电子造成的器件性能劣化和微细化后的多层配线以及结的电子迁移问题等等。由于微细化,随着高密度化一起而出现的损害可靠性的问题,这是必须认真加以解决的。比如采用三维元件结构,采用介电率高的薄膜解决α线问题;采用SOI结构,采用外延和开沟分离技术解决闭锁超载问题;采用降低电源电压,使器件结构高耐压化解决热电子造成的MOS特性劣化问题;采用高熔点金属配线,采用势垒金属层,表面平坦化措施解决电子迁移等问题。因此,主要的解决对策还是改善材料性能问题。

关于解决微细CMOS闭锁超载现象的对策和材料问题,若仅考虑闭锁超载现象,采用SOI结构就可确保完全无闭锁超载现象。而且SOI结构与体CMOS比较,在降低芯片面积、提高抗软漂移等方面的优越性大得多。但若从超LSI级SOI实用化角度考虑却还残留着许多尚未解决的课题。目前已进入实用化是SOS(双重异质外延法),同时对FIPOS(16K SRAM)和SIMOX(4K SRAM)等元件也进行了试验。元件进入微细化水平,只要稍微存在一点寄生电也会影响器件性能。

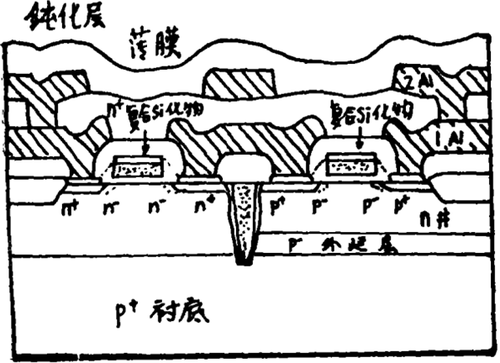

今后,为使器件高质量化高可靠性化,进一步积极推进SOI器件的实用化则是很有必要的。在体CMOS中,采用图3这种外延衬底和深沟分离二者并用的办法提高抗闭锁超载现象的能力是今后发展的方向。因而,有待于进一步提高高质量大直径外延硅片大量生产的技术水平(图3)。

图3:采用深沟分离的COMS截面图

兆位器件的性能和可靠性取决于配线、接触电阻以及它们的可靠性,这样说并不夸张。从小规模直到64 KDRAM的栅极材料都是使用的多晶硅,若集成度达到256 K时则必须使用复合层(硅化物/多晶硅双层),达到1 M位时就应当使用硅化物或纯金属方式,若到4M位时就必须要采用纯金属。目前集成度的水平下,栅极材料使用复合层最好,而将来到兆位集成度水平则将都要用纯金属栅极。作为栅极所使用的金属材料目前还仅仅只有W和Mo,这两种材料从很早以来就已开始被研究。但在高集成度的DRAM中,目前还没有达到实用化的阶段。其原因有技术上的困难也有至今可以用其它材料做成制品代替的原因,但在兆位时代则必须使用纯金属才行。通常对W和Mo都采用溅射法成膜工艺、把它们作栅极使用时,工艺上的主要问题是:一、对离子注入有屏蔽效应;二、有抗氧化性。最近已证实,W的阳极氧化膜厚度达到40 nm时,因其对离子注入的阻止能,就会能起到充分屏蔽的作用。另外,关于抗氧化性问题,若在加热时使用的保护气氛中添加适量的水,因栅极金属不会被氧化,就会出现对SiO2进行修复氧化。此外,目前金属膜的CVD技术也迅速发展起来了。使用WF6的WCVD具有(1)它在SiO2上很难生长而在Si,Al,硅化物等上面则可以择优生长;(2)生长温度低,最低可到350°C;(3)它可以应用减压CVD工艺,因而适宜于大量生产,分级复层的效果也较好;(4)同溅射法和电子束蒸发法比较,它可以获得栅极电阻很低的膜等特征,因而被认为是一项大有前途的技术。

随着微细化的发展,可靠性问题已成了必须解决的一个重要课题,而解决这个问题的根本所在就是要更深入地加强对器件工艺技术的理解。目前,日本的超LSI技术已经走在世界最前列,这也可从IEDM'84和ISSCC'85上日本的论文数目上看出来。在IEDM'84的98件论文中日本占34篇,在ISSCC'85的105篇论文中日本占49篇,所占比例是很大的。而在带有基础性技术如MOS的绝缘膜极限问题,微细化MOS器件物理,CMOS闭锁超载现象问题,个别关键技术等的研究来看,日本发表的论文大约占20%左右。要想在兆位时代居领先地位,还必须要突破许多技术难关,必须加强真正的基础研究工作和能产生出新技术的先行探索性工作。下面讨论几个具体问题。

薄型栅氧化膜的现状和课题

在微细化MOSFET中,由于短沟道化结构,会向栅氧化膜中注入热电子,使器件特性出现劣化现象。因此,对于微细化MOSFET使用的栅氧化薄膜,要求其俘获的热电子要少,比其它元件的膜的质量要高。除薄氧化膜能否付诸实用外,因耐压不好而使成品率下降也是要研究的问题之一。极力提高成品率是一个重要课题。

通常,干氧氧化膜中的俘获现象最少。但也有人认为造成薄的氧化膜耐压不好的弱斑,在干氧氧化的氧化膜中最多。但如果在干氧化前进行预处理,维持清洁的工艺过程,生长出优质的多晶硅膜,就可以获得到初期耐压特性良好的氧化薄膜。而初期特性好,长期可靠性也会好。另外,目前还存在的另一个问题是初期耐压重复性不好的问题。在工艺过程中,例如用RIE法形成多晶硅电极时,一加高压就会引起绝缘破坏。在离子注入形成源极、漏极时,栅极电荷增加也会引起绝缘破坏。像这类电荷增加现象,在工艺中各环节都可能造成,所以很有必要对工艺条件的最佳化和制造装置进行重新评价。即使是对生成的氧化薄膜的稳定可靠性,目前也还不能完全控制。前处理和后处理工程几乎全部过程对最终特性都有影响。所以很有必要同时从科学和技术两方面对制造工艺的可靠性、合理性等再次重新评价一下。

低温工艺技术

工艺过程的低温化对今后超LSI来说是很重要的。因为低温化能使得工艺过程之间的相互作用减少,使我们能够精确地控制工艺过程。因此,器件制造的自动化工艺线对实现将来的课题是必不可少的。最近许多研究机构报道了目前人们所关注的某些课题的研究结果,下面作一简要介绍。

最近对微波(2.45 GHz)ECR激发等离子氧化问题已开始进行探讨。把被激发的O2等离子输送到硅表面,在700℃—个小时条件下能生成23 nm的SiO2薄膜。用这种方法生成的Si-SiO2界面能级密度与在1000°C热氧化生成的薄膜具有几乎一样低的值。

用rf激发(0.5 ~ 3 MHz)的氧等离子氧化问题也进行了研究。用这种方法在的低温所获得的薄膜其电学特性就能与1100℃的热氧化膜比美。采用低温生长氧化膜的优点是:(一)残留应力小;(二)氧化中不会出现由于分凝而使硅中硼向SiO2膜中富集;(三)在局部氧化工艺中不会出现侧向氧化以及由氧化过程而产生硅晶体缺陷问题等。这些优点对今后精密加工工艺是非常有用的。

最近对光激发工艺也展开了热烈讨论。这种方法具有低温工艺的特长,如用ArF激发型激光器使硅表面氮化的方法。通常,硅氮化生长Si3N4膜时,要在1200°C热加工处理才能实现。采用NH3激光激发,在400℃就可以直接氮化,与热加工直接氮化相比,其绝缘性能极好。

硅外延生长晶体中也研究了光激发工艺的效果。其目的是想提高低温生长的外延单晶的结晶性能。用Hg-Xe灯照射作为光激发工艺的原过程,观察到了光子分解Si2H6和表面反应以及表面迁移的增强现象。即使是在700°C低温生长出的晶体,性能也相当好,该工艺今后大有发展前途。

另外,也报道了用紫外线照射生长SiO2膜时,即使不连续照射紫外线,SiO2膜也能连续堆积的所谓紫外线照射效应这一有趣的实验结果 · 使用KrF激发型激光器生长SiO2膜时,紫外线似乎只是对堆积初期有强烈影响。为证实这一观点,仅在生长初期照射10秒钟紫外光,SiO2膜开始堆积后就停止照射,发现膜仍能继续生长。这是个很重要的实验结果。其本质是什么?还有待于进一步探讨。

1985年末,估计能制出1M DRAM的样品,到3 ~ 4年后的1988年或1989年,估计4M DRAM可能达到实用化水平。从而逐步迈入超LSI时代。从80年代后期开始将要步入兆位时代了。4M DRAM要求真正的亚微米技术,这还有许多关键问题有待于突破。总之,面对兆位时代的挑战,应当进一步强调个别技术的飞速提高与总体技术可靠性提高的重要性。

[电子材料(日),1985年6月]